HDMI接口新增特殊分辨率时序

-

DRM 框架目前代码已经支持了绝大部分分辨率时序,但是部分 HDMI 屏幕旋转的场景下,可能还有一些特殊分辨率不支持。需要在 kernel\drivers\gpu\drm\drm_edid.c 中的drm_dmt_modes 的末尾新增项目:

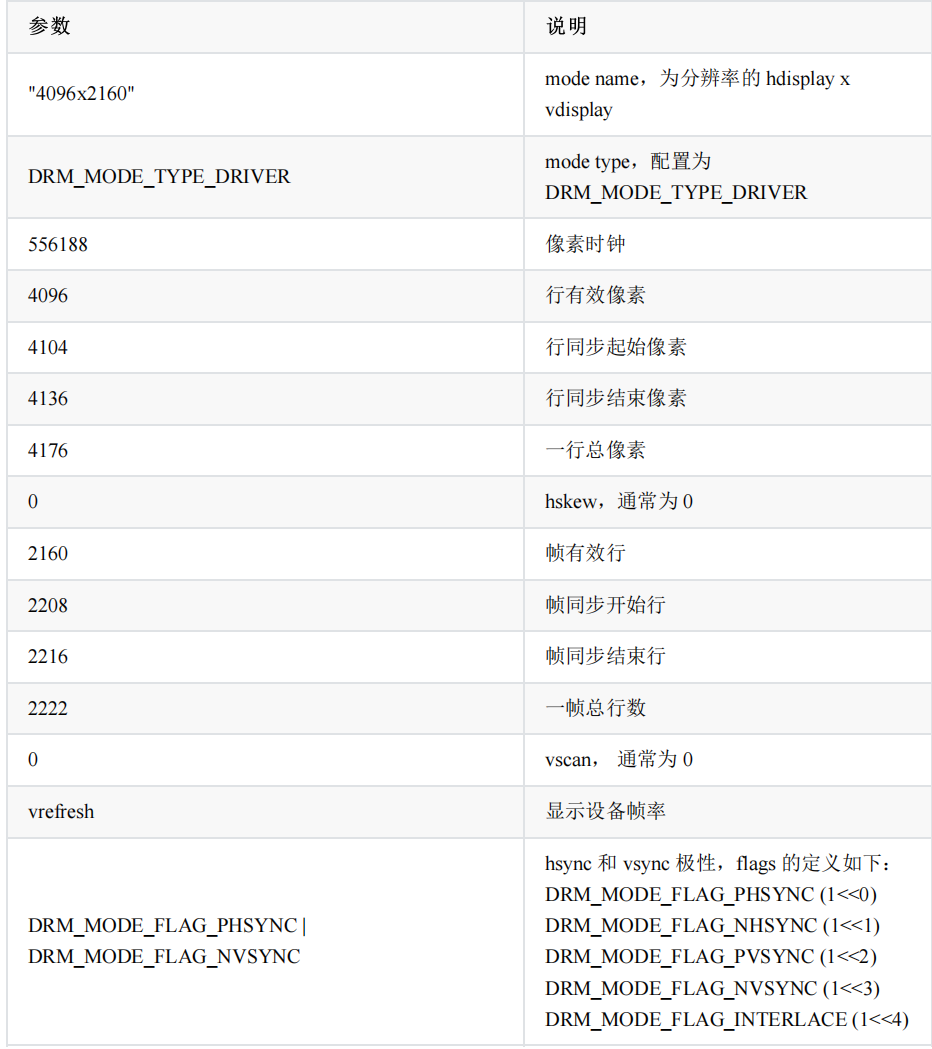

/* 0x58 - 4096x2160@59.94Hz RB */ { DRM_MODE("4096x2160", DRM_MODE_TYPE_DRIVER, 556188, 4096, 4104, 4136, 4176, 0, 2160, 2208, 2216, 2222, 0, DRM_MODE_FLAG_PHSYNC | DRM_MODE_FLAG_NVSYNC) },

-

@george 像素时钟 Pixel Clock 去查是三位数。。。是不是后面直接加三个零?

-

添加了下面 几行,然并卵

/* 0x59 - 3840x1080@120Hz RB */ { DRM_MODE("3840x1080", DRM_MODE_TYPE_DRIVER, 540000, 3840, 3848, 3880, 3920, 0, 1080, 1130, 1138, 1144, 0, DRM_MODE_FLAG_PHSYNC | DRM_MODE_FLAG_NVSYNC) }, /* 0x60 - 3840x1100@60Hz RB */ { DRM_MODE("3840x1100", DRM_MODE_TYPE_DRIVER, 282890, 3840, 3848, 3880, 3920, 0, 1100, 1118, 1126, 1132, 0, DRM_MODE_FLAG_PHSYNC | DRM_MODE_FLAG_NVSYNC) },edid信息如下

Detailed Timing Descriptors:

DTD 1: 3840x1100 59.998 Hz 192:55 68.998 kHz 282.890 MHz (1196 mm x 336 mm)

Hfront 48 Hsync 32 Hback 180 Hpol P

Vfront 3 Vsync 5 Vback 42 Vpol N

Display Range Limits:

Monitor ranges (GTF): 48-120 Hz V, 30-180 kHz H, max dotclock 600 MHz

DTD 2: 3840x1080 120.000 Hz 32:9 135.000 kHz 540.000 MHz (1196 mm x 336 mm)

Hfront 48 Hsync 64 Hback 48 Hpol P

Vfront 3 Vsync 10 Vback 32 Vpol N

Display Product Name: 'HDMI'

Extension blocks: 1

Checksum: 0x24我这应该怎么填?

-

https://www.cool-pi.com/topic/131/coolpi-4b-linux-kernel开发在线更新说明?_=1680497887440

用这个更新内核没错吧?? 似乎没啥效果啊

根据

DTD 1: 3840x1100 59.998 Hz 192:55 68.998 kHz 282.890 MHz (1196 mm x 336 mm) Hfront 48 Hsync 32 Hback 180 Hpol P Vfront 3 Vsync 5 Vback 42 Vpol N最终添加了一个

/* 0x59 - 3840x1100@60Hz RB */ { DRM_MODE("3840x1100", DRM_MODE_TYPE_DRIVER, 282890, 3840, 3888, 4068, 4224, 0, 1100, 1103, 1108, 1108, 0, DRM_MODE_FLAG_PHSYNC | DRM_MODE_FLAG_NVSYNC) }, -

@顾真牛 插拔HDMI然后打印dmesg发上来。

-

-

@顾真牛 改为动态分频测试一下

diff --git a/arch/arm64/boot/dts/rockchip/rk3588-cpcm5-evb.dts b/arch/arm64/boot/dts/rockchip/rk3588-cpcm5-evb.dts index da170f0b2086..3f01ba675516 100644 --- a/arch/arm64/boot/dts/rockchip/rk3588-cpcm5-evb.dts +++ b/arch/arm64/boot/dts/rockchip/rk3588-cpcm5-evb.dts @@ -1015,6 +1015,10 @@ &hdptxphy_hdmi0 { status = "okay"; }; +&hdptxphy_hdmi_clk0 { +status = "okay"; +}; + #if 1 &hdmi1 { enable-gpios = <&gpio4 RK_PB2 GPIO_ACTIVE_HIGH>; @@ -1044,6 +1048,10 @@ &route_hdmi1 { &hdptxphy_hdmi1 { status = "okay"; }; + +&hdptxphy_hdmi_clk1 { +status = "okay"; +}; #endif &dp0 { @@ -1304,6 +1312,8 @@ &uart2 { }; &display_subsystem { + clocks = <&hdptxphy_hdmi_clk0>, <&hdptxphy_hdmi_clk1>; + clock-names = "hdmi0_phy_pll", "hdmi1_phy_pll"; memory-region = <&drm_logo>; memory-region-names = "drm-logo"; };